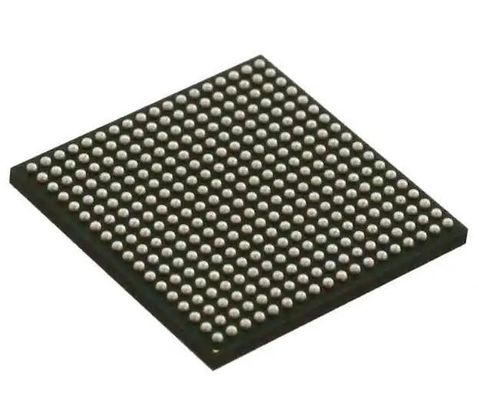

AM3352BZCZD30 Microprocesseur IC SitaraTM 1 noyau, 32 bits à 300 MHz 324-NFBGA (15x15)

Détails sur le produit:

| Lieu d'origine: | Originaux |

| Nom de marque: | original |

| Certification: | original |

| Numéro de modèle: | AM3352BZCZD30 |

Conditions de paiement et expédition:

| Quantité de commande min: | 1 |

|---|---|

| Prix: | negotiation |

| Détails d'emballage: | Boîte de carton |

| Délai de livraison: | 1 à 3 jours ouvrables |

| Conditions de paiement: | T/T |

| Capacité d'approvisionnement: | 100,000 |

|

Détail Infomation |

|||

| Nombre de noyaux/de largeur d'autobus: | 1 noyau, à 32 bits | Vitesse: | 300 MHz |

|---|---|---|---|

| Co-Processors/DSP: | Multimédia; NEON™ SIMD | RAM Controllers: | LPDDR, DDR2, DDR3, DDR3L |

| Contrôleurs d'affichage et d'interface: | LCD, écran tactile | Éthernet: | 10/100/1000Mbps (2) |

| USB: | USB 2,0 + PHY (2) | Tension - entrée-sortie: | 1.8V, 3.3V |

| Surligner: | IC de microprocesseur à 300 MHz AM3352BZCZD30,1 IC de microprocesseur AM3352BZCZD30,Pour les appareils de traitement des données |

||

Description de produit

AM3352BZCZD30 Microprocesseur IC SitaraTM 1 noyau, 32 bits à 300 MHz 324-NFBGA (15x15)

Les spécifications de Le numéro de téléphone est le numéro de téléphone de la personne concernée.

| Le type | Définition |

| Catégorie | Circuits intégrés (CI) |

| Incorporé | |

| Les microprocesseurs | |

| Mfr | Les instruments du Texas |

| Série | Pour les personnes âgées |

| Le paquet | Plateau |

| Statut du produit | Actif |

| Processeur de base | Le système de détection de l'infection doit être conforme aux exigences de la présente directive. |

| Nombre de cœurs/largeur du bus | 1 noyau, 32 bits |

| Vitesse | 300 MHz |

| Co-traitants/DSP | Multimédia; NEONTM SIMD |

| Contrôleurs de mémoire vive | Les données de référence sont les suivantes: |

| Accélération graphique | - Oui, oui. |

| Contrôleurs d'affichage et d'interface | Lcd, écran tactile |

| Éthernet | Le système de fréquence de l'appareil doit être équipé d'un système de fréquence de fréquence de l'appareil. |

| SATA | - |

| USB | Les données de connexion sont fournies par le système d'exploitation de l'Union. |

| Voltage - E/S | 1.8V, 3.3V |

| Température de fonctionnement | -40 °C à 90 °C (TJ) |

| Caractéristiques de sécurité | Cryptographie, générateur de nombres aléatoires |

| Type de montage | Monture de surface |

| Emballage / boîtier | 324-LFBGA |

| Paquet de dispositifs fournis par le fournisseur | Le nombre d'étoiles est de 324 NFBGA (15x15) |

| Interfaces supplémentaires | L'équipement doit être équipé d'un système de contrôle de l'équipement. |

| Numéro du produit de base | Le code est le suivant: AM3352 |

Caractéristiques duLe numéro de téléphone est le numéro de téléphone de la personne concernée.

• Jusqu'à 1 GHz pour le système SitaraTM ARM® Cortex

- A8 Processeur RISC 32 bits

– NEON™ SIMD Coprocessor

32KB d'instruction L1 et 32KB de cache de données avec détection d'erreur unique (parité)

256KB de cache L2 avec code de correction d'erreur (ECC)

176KB de ROM de démarrage sur puce

64KB de RAM dédiée

Émulation et débogage - JTAG

¢ Contrôleur d'interruption (jusqu'à 128 demandes d'interruption)

• Mémoire sur puce (RAM L3 partagée)

64 Ko de mémoire vive pour contrôleur de mémoire sur puce à usage général (OCMC)

¢ Accessible à tous les maîtres

¢ Prend en charge la rétention pour un réveil rapide

• Interfaces de mémoire externe

Le contrôleur de l'appareil doit être configuré de manière à ce que le système de contrôle de l'appareil puisse fonctionner correctement.

¢ mDDR: Horloge de 200 MHz (débit de données de 400 MHz)

DDR2: Horloge de 266 MHz (débit de données de 532 MHz)

¢ DDR3: Horloge à 400 MHz (débit de données à 800 MHz)

¢ DDR3L: Horloge à 400 MHz (débit de données à 800 MHz)

Le bus de données à 16 bits

1 Go d'espace adressable total

Prend en charge une configuration de périphérique de mémoire x16 ou deux x8

¢ Contrôleur de mémoire à usage général (GPMC)

Interface de mémoire asynchrone flexible à 8 bits et 16 bits avec jusqu'à sept sélections de puces (NAND, NOR, Muxed-NOR, SRAM)

Utilise le code BCH pour prendre en charge l'ECC à 4, 8 ou 16 bits

Utilise le code Hamming pour prendre en charge l'ECC à 1 bit

Module de localisation des erreurs (ELM)

Utilisé conjointement avec le GPMC pour localiser les adresses des erreurs de données à partir de polynômes de syndrome générés à l'aide d'un algorithme BCH

Prend en charge la localisation des erreurs de blocage de 4, 8 et 16 bits par bloc de 512 octets basé sur les algorithmes BCH

La mise en place deLe numéro de téléphone est le numéro de téléphone de la personne concernée.

• périphériques de jeu

• Automatisation domestique et industrielle

• Appareils médicaux de consommation

• Les imprimantes

• Systèmes de péage intelligents

• Machines à vendre connectées

• Les poids

• Les consoles pédagogiques

• Jouets de pointe

![]()