CD54HC299F3A IC Chip Shift Shift Register 1 bit 20-CDIP de l'élément 8

Détails sur le produit:

| Lieu d'origine: | original |

| Nom de marque: | original |

| Certification: | original |

| Numéro de modèle: | CD54HC299F3A |

Conditions de paiement et expédition:

| Quantité de commande min: | 1 |

|---|---|

| Prix: | negotiation |

| Détails d'emballage: | Boîte de carton |

| Délai de livraison: | jours 1-3working |

| Conditions de paiement: | T/T |

| Capacité d'approvisionnement: | 100 000 |

|

Détail Infomation |

|||

| Type de logique: | Inverseur | Nombre de circuits: | 6 |

|---|---|---|---|

| Nombre d'entrées: | 6 | Caractéristiques Schmitt: | Gâchette |

| Tension - approvisionnement: | 2V | 3.6V | Actuel - tranquille (maximum): | 1 µA |

| Actuel - sortie haute, bas: | 24mA, 24mA | Niveau logique d'entrée - Haut: | 1.3V | 2V |

| Délai de propagation max @ V, Max CL: | 6.2ns @ 3.3V, 50pF | Température de fonctionnement: | -55°C | 125°C |

| Surligner: | Puce de CD54HC299F3A IC,IC Chip Shift Shift Register,1 bit 20-CDIP de l'élément 8 |

||

Description de produit

Bit 20-CDIP de l'élément 8 du registre à décalage de décalage de puce de CD54HC299F3A IC 1

LOGIQUE À GRANDE VITESSE UNIV à 8 bits de CMOS

Caractéristiques de CD54HC299F3A

| TYPE | DESCRIPTION |

| Catégorie | Circuits intégrés (IC) |

| Logique | |

| Registres à décalage | |

| Mfr | Texas Instruments |

| Série | 54HC |

| Paquet | Tube |

| Statut de produit | Actif |

| Type de logique | Registre à décalage |

| Type de sortie | De trois états |

| Nombre d'éléments | 1 |

| Nombre de peu par élément | 8 |

| Fonction | Universel |

| Tension - approvisionnement | 2V | 6V |

| Température de fonctionnement | -55°C | 125°C (VENTRES) |

| Montage du type | Par le trou |

| Paquet/cas | 20-CDIP (0,300", 7.62mm) |

| Paquet de dispositif de fournisseur | 20-CDIP |

Caractéristiques de CD54HC299F3A

• Données d'entrée mises en tampon

• Quatre modes opérationnels : Décalage gauche, droit de décalage, charge et magasin

• Peut être cascadé pour des longueurs de Word de N-peu

• I/O0 - la capacité et le Trois-état d'entraînement de l'autobus I/O7 pour l'autobus ont orienté des applications

• FMAX typique = 50MHz à VCC = 5V, CL = 15pF, MERCI = 25oC

• Sortance (sur la température ambiante)

- Sorties standard…………… 10 charges de LSTTL

- Chauffeur de bus Outputs…………. 15 charges de LSTTL

• Grand choix de température de fonctionnement… -55oC à 125oC

• Retard de propagation et temps de transition équilibrés

• Réduction significative de puissance comparée à la logique IC de LSTTL

• Types de HC

- 2V à l'opération 6V

- Immunité de bruit élevée : ZÉRO = 30%, NIH = 30% de VCC à VCC = 5V

• Types de HCT

- 4.5V à l'opération 5.5V

- LSTTL direct a entré la compatibilité de logique,

VIL= 0.8V (maximum), VIH = 2V (minute)

- Le CMOS a entré la compatibilité, le ≤ 1µA au vol., VOH de l'IL

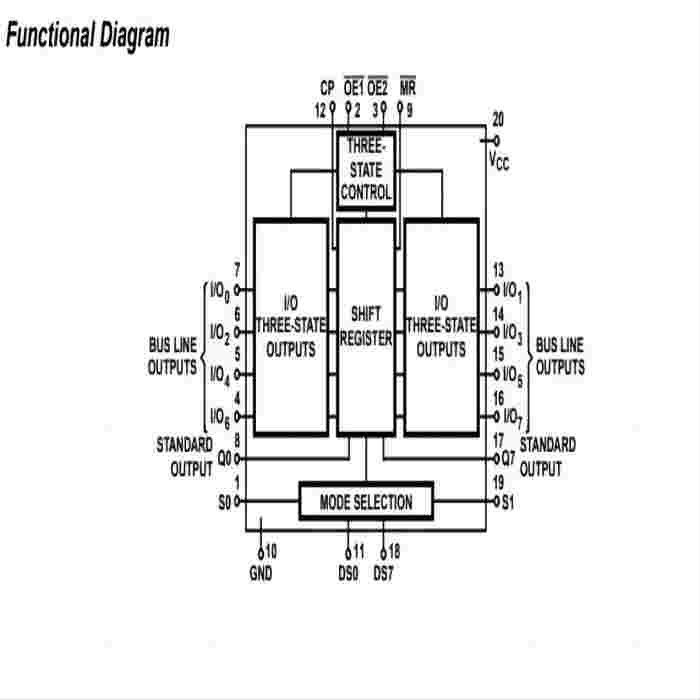

Descriptions de CD54HC299F3A

Les “HC259 et” les HCT299 sont décalage/inscriptions de stockage à 8 bits à la capacité d'interface de bus de trois-état. Le registre a quatre

modes de synchrone-fonctionnement commandés par les deux entrées choisies suivant les indications de la table choisie de mode (S0, S1). Le mode

choisi, les données périodiques (DS0, DS7) et les données parallèles (I/O0- I/O7) répondre seulement à la transition à hauteur basse de l'horloge

Impulsion (CP). S0, S1 et entrées de données doivent être un temps installé stable avant la transition positive d'horloge.

Classifications environnementales et d'exportation de CD54HC299F3A

| ATTRIBUT | DESCRIPTION |

| Statut de RoHS | ROHS3 conforme |

| Niveau de sensibilité d'humidité (MSL) | Non applicable |